【応用情報】コンピュータの五大装置と命令実行サイクルを解説

この記事では、コンピュータの五大装置と命令実行サイクルについて、初心者にも分かりやすく、図解付きで丁寧に解説しています!

コンピュータの五大装置

- 制御装置・演算装置・記憶装置・入力装置・出力装置を合わせて五大装置と呼ぶ。制御装置と演算装置は合わせてCPUと呼ぶ。

- CPUと記憶装置がやり取りしながら命令を実行する手順を命令実行サイクルと呼ぶ。

命令実行サイクル

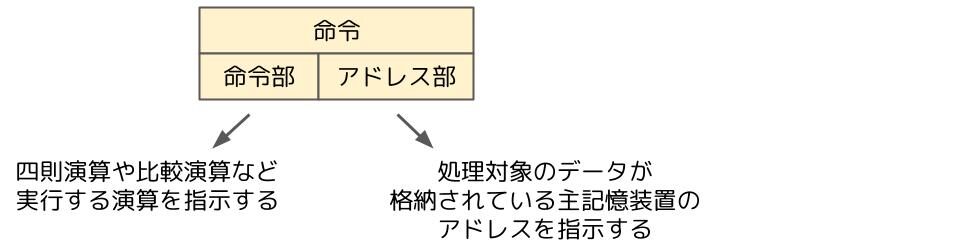

- 命令は命令の内容を表す命令部と命令に必要なデータが主記憶装置のどこに格納されているかを表すアドレス部に分かれる。

- 命令レジスタは主記憶装置から取り出した命令を格納する。

- 命令アドレスレジスタは次に実行する命令のアドレス(主記憶装置のどこに格納されているか)を格納する。

- アドレスレジスタは命令の実行に必要なデータのアドレスを格納する。

- 解読器(デコーダ)は命令レジスタの命令を解読する。

- CPUは①命令フェッチ→②命令の解読→③実効アドレス計算→④オペランド読出し→⑤命令の実行、の順番で命令を実行する。

コンピュータの五大装置

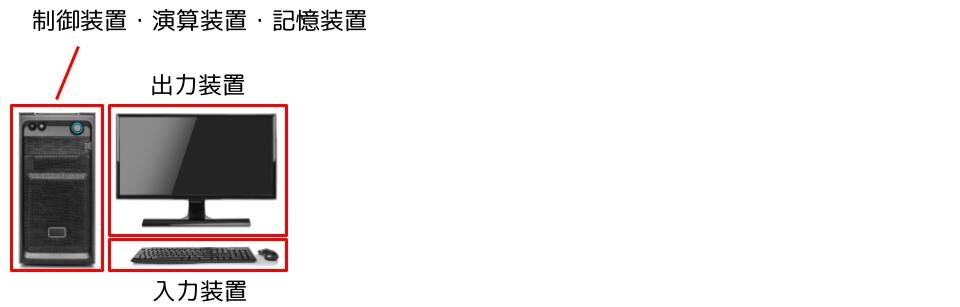

コンピュータは、制御装置・演算装置・記憶装置・入力装置・出力装置の五つの装置から構成されています。制御装置と演算装置を合わせてCPUと言います。

入力装置と出力装置は分かりやすいですね。

入力装置はマウスやキーボードなど、人間がコンピュータにデータや命令を入力するための装置で、出力装置はディスプレイなど、コンピュータが処理した結果を出力するための装置です。

制御装置・演算装置・記憶装置は人間が触ったり見たりする必要が無いので、筐体と呼ばれる箱に入れて保護されています。

五大装置にはそれぞれ以下の役割があります。

| 制御装置 | 記憶装置にある命令を取得・解読し、他の装置に命令を伝達する装置。 その名の通り、他の装置を制御している。 |

|---|---|

| 演算装置 | 記憶装置にあるデータから足し算・引き算などの四則演算や大小比較などの比較演算といった演算を行う装置。計算結果は記憶装置に返す。 |

| 記憶装置 | データや処理内容であるプログラムを記憶する装置。 記憶装置には主記憶装置と補助記憶装置がある。 |

| 入力装置 | コンピュータの外部からデータや命令を指示する装置。 |

| 出力装置 | コンピュータの処理結果を外部に表示・出力する装置。 |

GPU

コンピュータにはGPUと呼ばれる頭脳も存在します。CPUが複雑な処理やコンピュータ全体の制御を行う一方で、GPUは画像処理の高速化など、グラフィック処理を担当します。

記憶装置には主記憶装置と補助記憶装置がある

記憶装置には主記憶装置と補助記憶装置があります。主記憶装置はメインメモリとも言います。

主記憶装置はコンピュータが動くために必要なプログラムやデータを一時的に記憶する装置です。CPUとやり取りできるほど処理が速いですが、電源が消えると記録している情報も消えるという特徴があります。

補助記憶装置はプログラムやデータをずっと保持する装置です。処理は遅いですが、電源が消えても記録している情報はそのまま保持出来ます。長期的に記録したい場合に使います。USBやハードディスクなどが補助記憶装置ですね。

データと制御の流れ

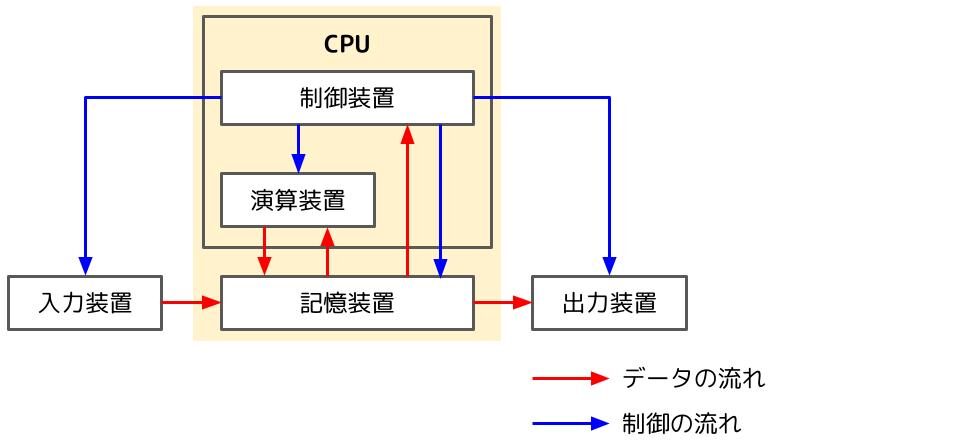

コンピュータの中では、五大装置が助け合いながらデータを処理していきます。

下の絵はデータと制御の流れをざっくり表したものです。

制御の流れはとてもシンプルで分かりやすいですね。

制御装置が全ての装置を制御しています。制御装置が記憶装置にデータの記録を指示したり、出力装置にデータを出力するように指示します。

データの流れも入力装置と出力装置は分かりやすいですね。

入力装置と出力装置はそれぞれデータの入り口と出口になっています。

- 入力装置を通じて人間が入力した命令やデータは記憶装置に保管されます。

- CPUが記憶装置とやり取りしながら演算を行い、最終的に出て来た結果を記憶装置に保管します。(命令実行サイクル)

- 記憶装置に保管された演算結果が出力装置から出力されます。

②ではCPUと記憶装置がデータをやり取りしながら演算を行い、最後には演算結果を記憶装置に保管します。この時の手順を命令実行サイクルと言います。

ユニファイドメモリ方式

従来はCPU用メモリとGPU用メモリは別々で、主記憶装置はCPU用のメモリでした。ユニファイドメモリ方式を採用すると、GPUも主記憶装置の一部を使えるようになります。グラフィック処理に主記憶装置を使えるということです。

ユニファイドメモリ方式を使うとCPU用メモリとGPU用メモリの間のデータ移動が不要になります。例えば、CPUが前処理したデータをGPUがグラフィック処理するとき、従来はCPU用メモリとGPU用メモリの間でデータを行き来させる必要がありましたが、ユニファイドメモリ方式を使えばデータの行き来が必要なくなり、処理速度が上がります。

命令の構成と命令実行サイクル

CPUが「1+2」という処理をするとき、「足し算をしなさい」という命令と、足し算に使う「1」と「2」というデータが必要です。

こんな感じでCPUが処理する命令は、

どんな処理をして欲しいかを表す「命令部」と処理の対象となるデータが主記憶装置のどこに格納されているかを表す「アドレス部」で構成されます。アドレス部はオペランド部とも呼びます。

命令実行サイクル

では、CPUはこんな命令をどういう手順で実行するのでしょうか?

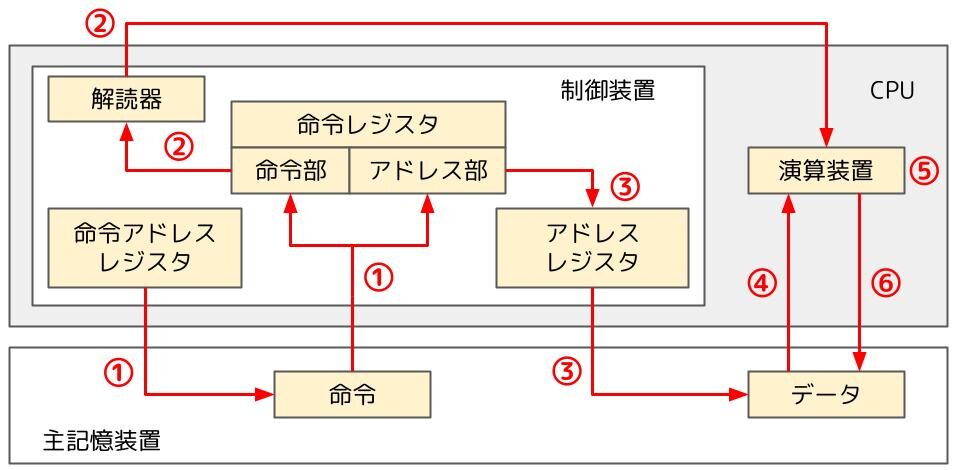

その手順を命令実行サイクルと呼び、命令実行サイクルの大まかな流れは、ざっくり下のようになります。

制御装置の中には様々なレジスタ・装置が入ってますが、代表的なものはこの4つです。

- 命令レジスタ:主記憶装置から取り出した命令を格納する。

- 命令アドレスレジスタ:次に実行する命令が、主記憶装置のどのアドレスに格納されているか記録する。プログラムカウンタとも呼ぶ。

- アドレスレジスタ:演算に必要なデータが、主記憶装置のどのアドレスに格納されているか記録する。

- 解読器(デコーダ):命令レジスタに格納された命令の命令部を解読する。

では、改めて命令実行サイクルで何をしているか、見てみましょう。

| ① 命令フェッチ | 命令アドレスレジスタの情報をもとに、主記憶装置から命令を取り出して命令レジスタに格納する。 |

|---|---|

| ② 命令の解読 | 制御装置の解読器が命令の命令部を解読し、演算装置に指示する。 |

| ③ 実効アドレス計算 | 命令のアドレス部をアドレスレジスタに送り、命令の実行に 必要なデータが主記憶装置のどこに格納されているか指示する。 |

| ④ オペランド読出し | アドレスレジスタに格納されているアドレス部の情報をもとに、 主記憶装置から、命令に必要なデータを演算装置に送る。 |

| ⑤ 命令の実行 | 演算装置が命令を実行する。 |

| ⑥ 演算結果格納 | 演算結果を主記憶装置に格納する。 |

応用情報技術者試験での出題例

令和7年度秋期問9、令和5年度秋期問11

応用情報技術者

午前試験 令和7年度秋期問9、令和5年度秋期問11

画像表示用フレームバッファがユニファイドメモリ方式であるシステムの特徴はどれか。

ア 主記憶とは別に専用のフレームバッファをもつ。

イ 主記憶の一部を表示領域として使用する。

ウ シリアル接続した表示デバイスに,描画コマンドを用いて表示する。

エ 表示リフレッシュが不要である。

正解は”イ”

従来はCPU用メモリとGPU用メモリは別々で、主記憶装置はCPU用のメモリでした。ユニファイドメモリ方式を採用すると、GPUも主記憶装置の一部を使えるようになります。グラフィック処理に主記憶装置を使えるようになるということですね。よって答えはエです。

令和6年度秋期問8

応用情報技術者

午前試験 令和6年度秋期問8

RISCプロセッサの5段パイプラインの命令実行制御の順序はどれか。ここで,このパイプラインのステージは次の五つとする。

① 書込み

② 実行とアドレス生成

③ 命令デコードとレジスタファイル読出し

④ 命令フェッチ

⑤ メモリアクセス

ア ③,④,②,⑤,①

ウ ④,③,②,⑤,①

イ ③,⑤,②,④,①

エ ④,⑤,③,②,①

正解は”ウ”

プロセッサはCPUと同じ意味と捉えて問題ありません。

CPUの命令実行制御の順番は、次の通りです。

①命令フェッチ:主記憶装置から実行する命令を取り出し、命令レジスタに記録する。

②命令デコードとレジスタファイル読出し:命令レジスタに格納した命令を解読器でデコードし、演算に必要なデータの格納場所を記録しているアドレスレジスタから読出します。

③実行とアドレス生成:演算装置が演算を実行し、演算結果を格納するアドレスを生成します。

④メモリアクセス:演算結果を格納するために主記憶装置にアクセスします。

⑤書込み:主記憶装置に演算結果を格納する。

令和3年度秋期問15

応用情報技術者

午前試験 令和3年度秋期問15

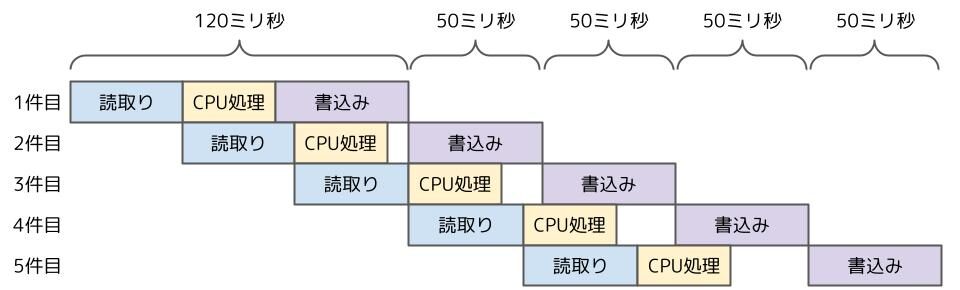

1件のデータを処理する際に,読取りには40ミリ秒,CPU処理には30ミリ秒,書込みには50ミリ秒掛かるプログラムがある。このプログラムで,n件目の書込みと並行してn+1件目のCPU処理とn+2件目の読取りを実行すると,1分当たりの最大データ処理件数は幾つか。ここで,OSのオーバーヘッドは考慮しないものとする。

ア 500 イ 666 ウ 750 エ 1,200

正解は”エ”

読取り・CPU処理・書込みは並行して実行できます。1件目から5件目まで書いてみると、最後の書込み処理に時間が掛かるため、結局、書込み処理の行列が出来てしまうことが分かります。

1分=60,000ミリ秒です。1件目を除くと60,000ミリ秒÷50ミリ秒=1200件なので、答えはエです。