【基本情報】初心者にも分かりやすく!キャッシュメモリの全てを解説

この記事では、キャッシュメモリについて、初心者にも分かりやすく、図解付きで丁寧に解説しています!

キャッシュメモリ

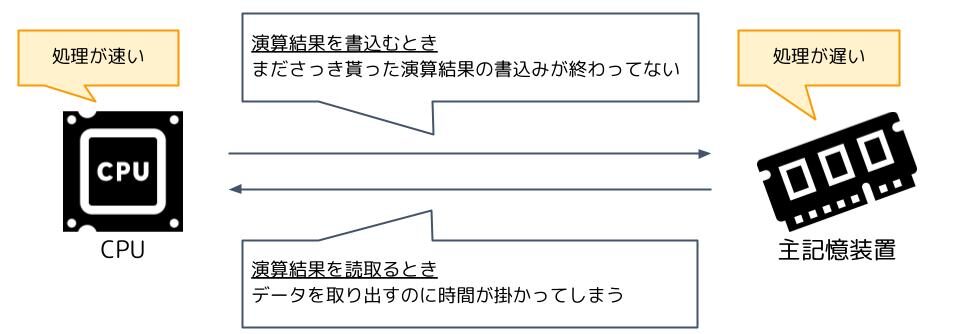

- CPUは主記憶装置とやり取りしながら命令を処理するが、主記憶装置はCPUと比べて処理速度が遅い。

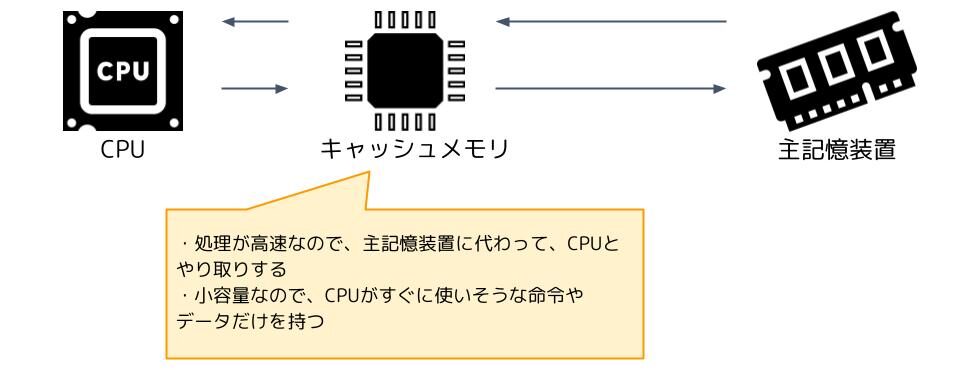

- キャッシュメモリはCPUと主記憶装置の間に入って、主記憶装置の代わりにCPUとデータのやり取りをする。

- CPUがキャッシュメモリにアクセスした時に目的のデータがある確率をヒット率、CPUが目的のデータにアクセスできる実際の平均時間を実効アクセス時間と呼ぶ。

- ライトスルー方式は、キャッシュメモリと主記憶装置に同時にデータを書込む方式。

- ライトバック方式は、普段はキャッシュメモリにだけデータを書込み、キャッシュメモリからデータを追い出す時に主記憶装置にデータを書込む。

CPUは主記憶装置とやり取りする

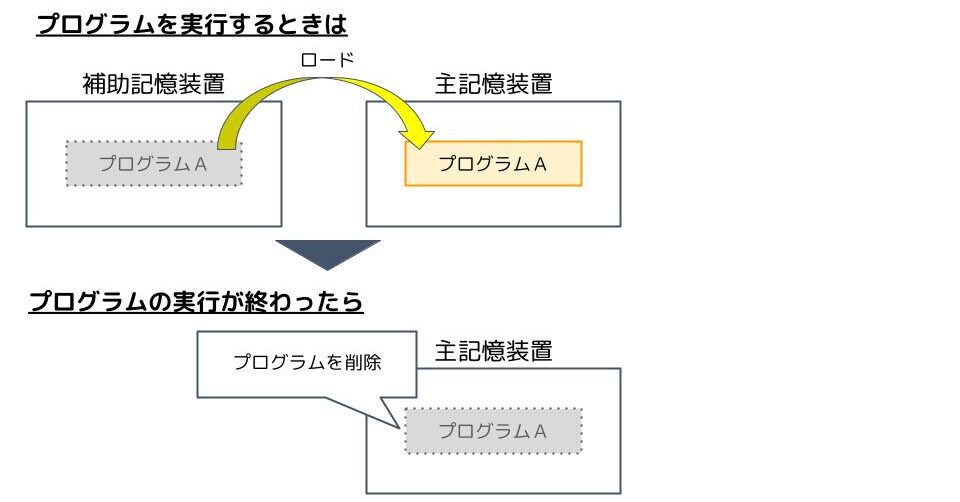

私たちが使うプログラムは、普段、補助記憶装置に記録されており、プログラムを実行する時は主記憶装置へロードしてから実行します。

CPUは主記憶装置に置かれたプログラムの命令とデータを取り出して演算します。

また、CPUが演算した結果は主記憶装置に格納しておきます。

CPUが主記憶装置とやり取りしながら命令を実行する手順は命令実行サイクルと呼ばれます。命令実行サイクルについて詳しく知りたい方はこちらの記事をご覧ください。

ここで押さえておいて欲しいのは、

プログラムを実行する時、CPUと主記憶装置が命令やデータのやり取りをしているということです!

しかし、主記憶装置の処理速度はCPUに比べてかなり遅いため、CPUに待ち時間が発生し、処理効率が悪くなってしまいます。

ここで出てくるのがキャッシュメモリです!

キャッシュメモリの役割

キャッシュメモリは主記憶装置より小容量ですが、処理が高速です。

キャッシュメモリは、遅い主記憶装置に代わって、CPUで命令やデータのやり取りをします。ただ、小容量なので、キャッシュメモリには、CPUがすぐに使いそうな命令やデータしか保管しません。

キャッシュメモリはすぐに使いそうな命令やデータしか持たないので、

不幸にもCPUが今すぐ欲しい!データを持っていないこともあるんですね。

その場合は、CPUも諦めて主記憶装置に欲しいデータを取りに行きます。

- CPUは最初にキャッシュメモリに欲しいデータを取りに行く

- キャッシュメモリにデータが無かったら、主記憶装置にデータを取りに行く

- ②で取りに行ったデータはキャッシュメモリに記録しておく

こうすることで、次に同じデータを取りに行くとき、速く取れるようになる

主記憶装置とキャッシュメモリの違いと言えば、DRAMとSRAMもありますね!

それはこちらの記事で解説しています!

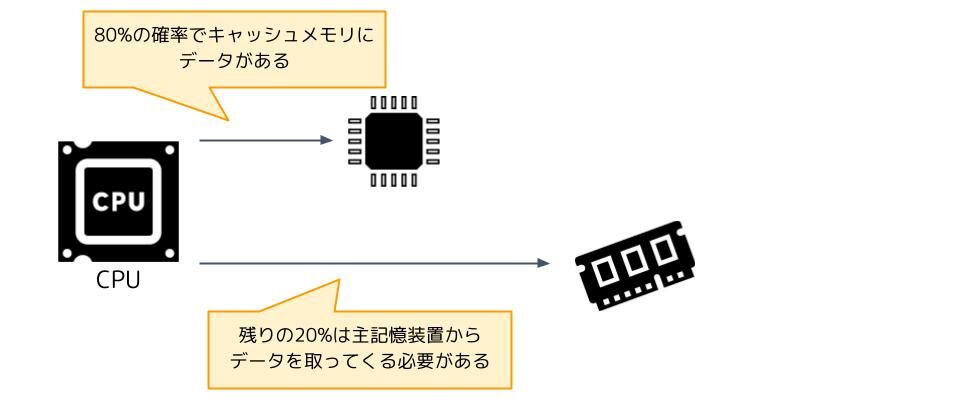

ヒット率と実効アクセス時間

キャッシュメモリは目的のデータを持っているとは限りません。

キャッシュメモリが目的のデータを持っている確率をヒット率と呼びます。

ヒット率が80%だとすると、CPUは20%の確率で主記憶装置にデータを取りに行く必要があります。

実効アクセス時間は、キャッシュメモリを導入した場合、CPUがどれだけの時間でデータにアクセス出来るかを示した数字です。

①キャッシュメモリへのアクセスに全部で掛かった時間

キャッシュメモリへのアクセス時間×ヒット率

②主記憶装置へのアクセスに全部で掛かった時間

主記憶装置へのアクセス時間×(1-ヒット率)

実効アクセス時間=①+②

例えば、ヒット率が80%、キャッシュメモリへのアクセス時間が20ナノ秒、

主記憶装置へのアクセス時間が50ナノ秒の場合の実効アクセス時間は26ナノ秒です。

①キャッシュメモリへのアクセスに全部で掛かった時間

20ナノ秒×80%=16ナノ秒

②主記憶装置へのアクセスに全部で掛かった時間

50ナノ秒×20%=10ナノ秒

実効アクセス時間=16ナノ秒+10ナノ秒=26ナノ秒

主記憶装置への書込み方式

キャッシュメモリはCPUが演算した結果を貰う役割も持っています。

ただし、キャッシュメモリはあくまでも主記憶装置の補助役なので、最終的には主記憶装置に演算結果を渡す必要があります。

では、どのタイミングでキャッシュメモリは主記憶装置にデータを書込むのでしょうか?

主記憶装置への書込み方式にはライトスルー方式とライトバック方式があります。

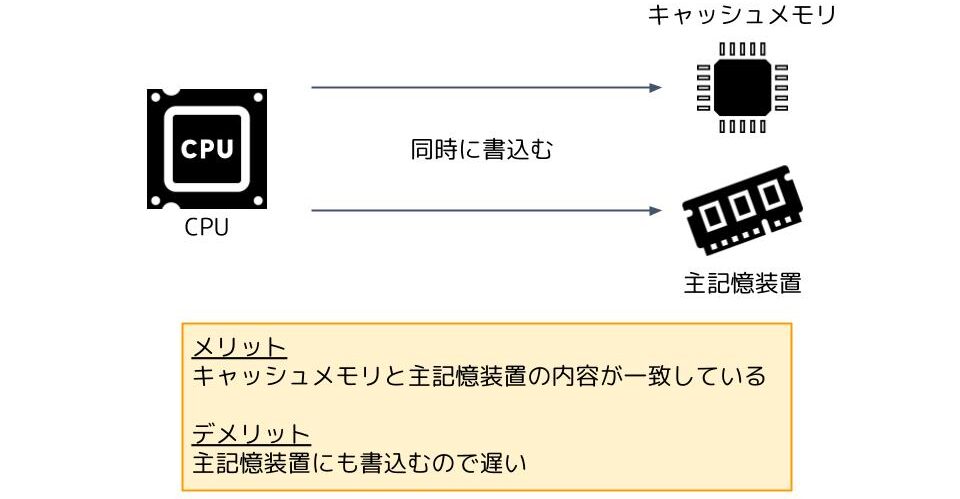

ライトスルー方式

ライトスルー方式は、キャッシュメモリと主記憶装置に同時にデータを書込む方式です。

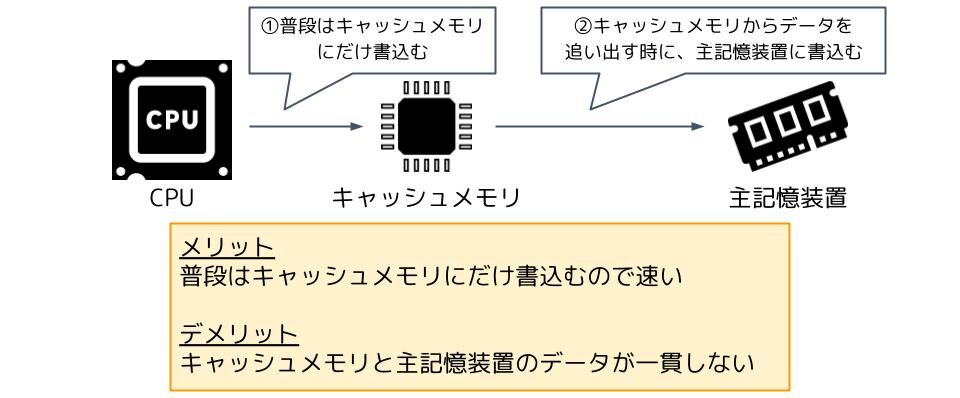

ライトバック方式

ライトバック方式では、普段はキャッシュメモリにしかデータを書込みません。

キャッシュメモリの容量がいっぱいになってきて、データを追い出すタイミングで、

主記憶装置への書込みを行います。

基本情報技術者試験での出題例

令和6年度問3

基本情報技術者

科目A 令和6年度問3

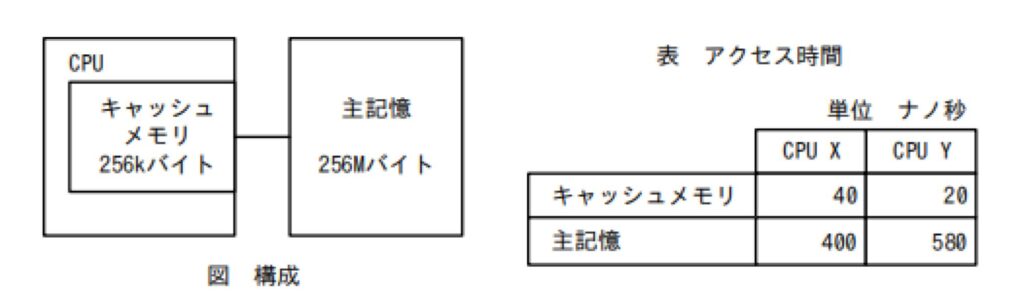

図に示す構成で,表に示すようにキャッシュメモリと主記憶のアクセス時間だけが異なり,他の条件は同じ2種類のCPU XとYがある。

あるプログラムをCPU XとYとそれぞれ実行したところ,両者の処理時間が等しかった。このとき,キャッシュメモリのヒット率は幾らか。ここで,CPU以外の処理に影響はないものとする。

ア 0.75 イ 0.90 ウ 0.95 エ 0.96

正解は”イ”

キャッシュメモリのヒット率をαとすると、

CPU Xの処理時間:40α+(1-α)×400=400-360α(ナノ秒)

CPU Yの処理時間:20α+(1-α)×580=580-560α(ナノ秒)

今、CPU XとCPU Yの処理時間が同じなので、

400-360α=580-560αとなり、α=0.90となり、答えはイ。

サンプル問題問12、平成31年度春期問10

基本情報技術者

科目A サンプル問題問12、午前試験 平成31年度春期問10

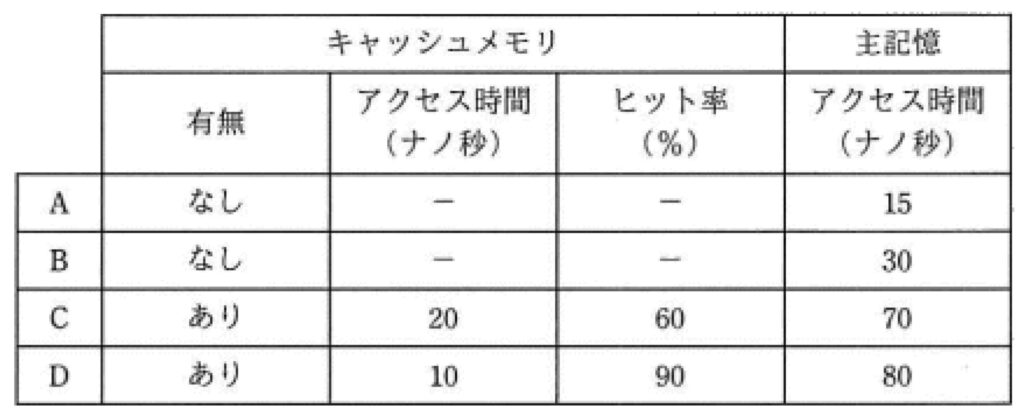

A~Dを,主記憶の実効アクセス時間が短い順に並べたものはどれか。

ア A, B, C, D イ A, D, B, C

ウ C, D, A, B エ D, C, A, B

正解は”イ”

それぞれの実効アクセス時間は以下の通りです。

A:15ナノ秒

B:30ナノ秒

C:20ナノ秒×0.6+70ナノ秒×0.4=40ナノ秒

D:10ナノ秒×0.9+80ナノ秒×0.1=17ナノ秒

平成30年度春期問11

基本情報技術者

午前試験 平成30年度春期問11

キャッシュメモリに関する記述のうち,適切なものはどれか。

ア キャッシュメモリにヒットしない場合に割込みが生じ,プログラムによって主記憶からキャッシュメモリにデータが転送される。

イ キャッシュメモリは,実記憶と仮想記憶とのメモリ容量の差を埋めるために採用される。

ウ データ書込み命令を実行したときに,キャッシュメモリと主記憶の両方を書き換える方式と,キャッシュメモリだけを書き換えておき,主記憶の書換えはキャッシュメモリから当該データが追い出されるときに行う方式とがある。

エ 半導体メモリのアクセス速度の向上が著しいので,キャッシュメモリの必要性は減っている。

正解は”ウ”

キャッシュメモリを導入した場合の主記憶装置にデータを書込む方式には、

- ライトスルー方式:キャッシュメモリと主記憶装置に同時にデータを書込む

- ライトバック方式:普段はキャッシュメモリにデータを書込んで、キャッシュメモリからデータを追い出すときに、主記憶装置にデータを書込む

があります。よって答えはウです。

平成29年度春期問9

基本情報技術者

午前試験 平成29年度春期問9

キャッシュの書込み方式には,ライトスルー方式とライトバック方式がある。ライトバック方式を使用する目的として,適切なものはどれか。

ア キャッシュと主記憶の一貫性(コヒーレンシ)を保ちながら,書込みを行う。

イ キャッシュミスが発生したときに,キャッシュの内容の主記憶への書き戻しを不要にする。

ウ 個々のプロセッサがそれぞれのキャッシュをもつマルチプロセッサシステムにおいて,キャッシュ管理をライトスルー方式よりも簡単な回路構成で実現する。

エ プロセッサから主記憶への書込み頻度を減らす。

正解は”エ”

プロセッサはCPUのことです。

ライトバック方式は、普段キャッシュメモリにだけ書込みを行い、データを追い出す時に主記憶装置にデータを書込みするので、ライトスルー方式に比べて主記憶装置への書込みの回数を減らすことが出来ます。

平成28年度春期問11

基本情報技術者

午前試験 平成28年度春期問11

キャッシュメモリの効果として,適切なものはどれか。

ア 主記憶からキャッシュメモリへの命令の読出しと,主記憶からキャッシュメモリへのデータの読出しを同時に行うことによって,データ転送を高速に行う。

イ 主記憶から読み出したデータをキャッシュメモリに保持し,CPUが後で同じデータを読み出すときのデータ転送を高速に行う。

ウ 主記憶から読み出したデータをキャッシュメモリに保持し,命令を並列に処理することによって演算を高速に行う。

エ 主記憶から読み出した命令をキャッシュメモリに保持し,キャッシュメモリ上でデコードして実行することによって演算を高速に行う。

正解は”イ”

キャッシュメモリは主記憶装置から読みだしたデータを保持します。

そうすることで、同じデータをCPUが求めてきた時に、速くデータを渡せるようになるんですね。