この記事ではキャッシュメモリについてIT初心者にも分かりやすく解説します。

キャッシュメモリとは

- キャッシュメモリとは、主記憶装置の代わりにCPUと情報のやり取りをする記憶装置。

- 実効アクセス時間とは、CPUが実際に欲しい情報にアクセスすることが出来る時間。

- ライトスルー方式とは、CPUが情報を書き込むときに、主記憶装置とキャッシュメモリの両方同時に書き込む方式。

- ライトバック方式とは、CPUが情報を書き込むときに、まずキャッシュメモリだけに書き込みを行い、その後、主記憶装置に書き込む方式。

基本情報ではキャッシュメモリに関する問題が頻出します。是非最後までご覧ください。

キャッシュメモリ

キャッシュメモリとは、主記憶装置(メインメモリ)の代わりにCPUとデータのやり取りをする記憶装置です。

CPUはプログラム実行するとき、主記憶装置から必要なデータや命令受け取ります。

しかし、主記憶装置の処理速度はそんなに速くないです。そのため、CPUの性能が向上し処理速度が上がると、主記憶装置ではデータのやり取りが間に合わなくなりました。

ここで登場するのがキャッシュメモリです。

主記憶装置よりも処理速度が速いキャッシュメモリがCPUとデータのやり取りをすることで、CPUの処理速度に合わせることにしたのです。

しかし、キャッシュメモリは主記憶装置より処理速度が速い代わりに容量が少ないという欠点があります。

なので、CPUが必要なデータを全て持っている訳ではありません。必要に応じて主記憶装置ともやり取りをしないといけないのです。

そこで、CPUは以下のような手順で処理を行うことにしました。

- キャッシュメモリに必要なデータがあるか確認する

- 必要なデータがあればキャッシュメモリからデータをもらう

- 必要なデータが無ければ主記憶装置からデータをもらう

- 主記憶装置からデータをもらう時は、キャッシュメモリにもそのデータを保存する

④でキャッシュメモリにもデータを保存する理由は、再びそのデータが必要になった時にキャッシュメモリにあった方が受け渡しが速くて便利だからです。

実効アクセス時間

キャッシュメモリを導入することで、どれだけ速くデータのやり取りが出来るようになったのかはとても大切な指標になります。データのやり取りの速さは実効アクセス時間で表します。

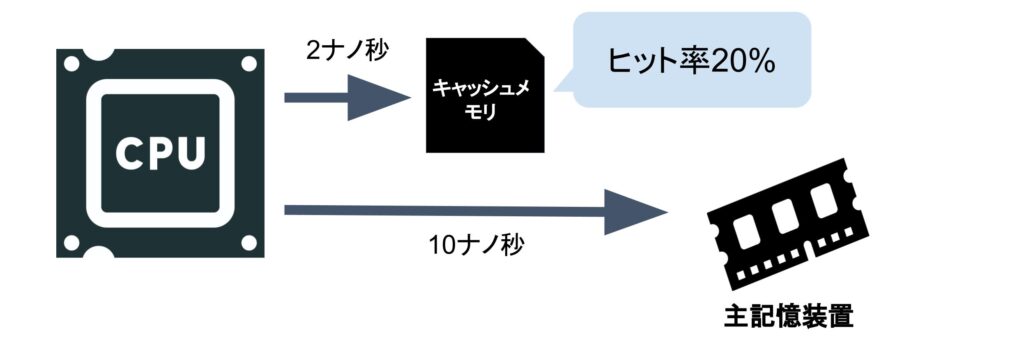

下図のようにCPUが主記憶装置とだけデータをやり取りする場合の実効アクセス時間は10ナノ秒となります。

主記憶装置へのアクセスに10ナノ秒、キャッシュメモリへのアクセスに2ナノ秒掛かり、CPUが欲しいデータの内、20%がキャッシュメモリにある場合、

20%はキャッシュメモリ、80%は主記憶装置とアクセスすれば良いので、

実効アクセス時間=(2ナノ秒×0.2)+(10ナノ秒×0.8)=8.4ナノ秒となります。

ちなみに、CPUが欲しいデータがキャッシュメモリに存在する確率をヒット率と言います。

主記憶装置だけの場合の実効アクセス時間は10ナノ秒だったので、処理速度を16%も削減できたことになります。

また、以上のことから、実効アクセス時間の公式が次のように書けることが分かります。

実効アクセス時間 = (キャッシュメモリへのアクセス時間 × ヒット率) +

平均アクセス時間 = (主記憶装置へのアクセス時間 × (1-ヒット率)) +

キャッシュメモリにデータが存在する時はキャッシュメモリとアクセスして、キャッシュメモリにデータが存在しない時は主記憶装置とアクセスするという意味の公式ですね。

主記憶装置への書き込み

CPUが処理を実行した結果は主記憶装置に書き込まれます。キャッシュメモリにだけ書き込めば良いのでは?と思うかもしれませんが、キャッシュメモリでは容量が足りないので主記憶装置にも書き込む必要があります。

では、CPUが処理を実行した結果をキャッシュメモリが受け取って、どのように主記憶装置へ書き込まれるのでしょうか?「ライトスルー方式」と「ライトバック方式」の2つの方法があります。

ライトスルー方式

ライトスルー方式とは、CPUがキャッシュメモリに書き込み処理を行う際、主記憶装置へも同時に書き込む方式です。

ライトスルー方式は、書き込み処理に時間が掛かる主記憶装置にも同時に書き込みを行います。なので、書き込み処理に時間が掛かりますが、キャッシュメモリと主記憶装置のデータは常に一致しており、データの一貫性を保つことが出来ます。

メリット :キャッシュメモリと主記憶装置の間でデータの一貫性を保てる

デメリット:書き込み処理に時間が掛かる

ライトバック方式

ライトバック方式とは、キャッシュメモリに書き込み処理を行った後に、まとめて主記憶装置に書き込み処理を行う方式です。

ライトバック方式は、キャッシュメモリに先に書き込みを行い、後からまとめて主記憶装置に書き込みます。

なので、書き込み処理は速く完了しますが、停電等でキャッシュメモリのデータが消えてしまうと、データが主記憶装置に保存されておらず、データをロストしてしまう可能性があります。

メリット :書き込み処理が速く完了する

デメリット:キャッシュメモリと主記憶装置の間でデータが一貫せず、データをロストしてしまう可能性がある

基本情報技術者試験での出題例

令和6年度問3

基本情報技術者

科目A 令和6年度問3

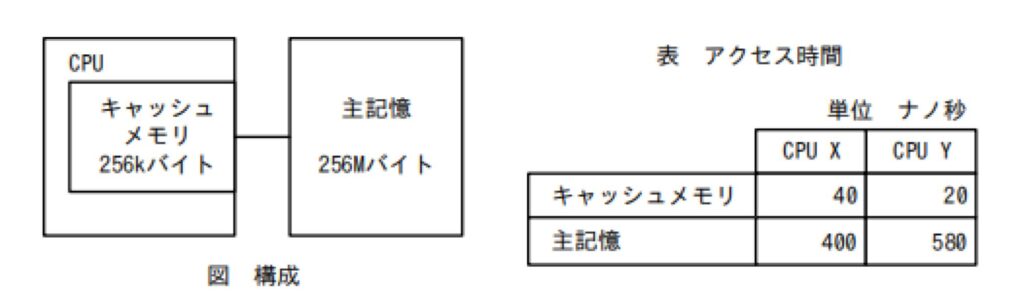

図に示す構成で,表に示すようにキャッシュメモリと主記憶のアクセス時間だけが異なり,他の条件は同じ2種類のCPU XとYがある。

あるプログラムをCPU XとYとそれぞれ実行したところ,両者の処理時間が等しかった。このとき,キャッシュメモリのヒット率は幾らか。ここで,CPU以外の処理に影響はないものとする。

ア 0.75 イ 0.90 ウ 0.95 エ 0.96

正解は”イ”

キャッシュメモリのヒット率をαとすると、

CPU Xの処理時間:40α+(1-α)×400=400-360α(ナノ秒)

CPU Yの処理時間:20α+(1-α)×580=580-560α(ナノ秒)

今、CPU XとCPU Yの処理時間が同じなので、

400-360α=580-560αとなり、α=0.90となり、答えはイ。

平成31年度春期問10

基本情報技術者

午前試験 平成31年度春期問10

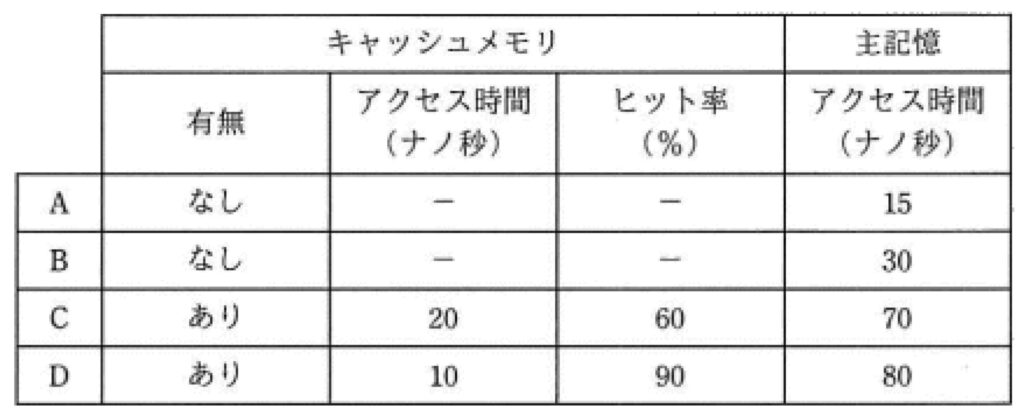

A~Dを,主記憶の実効アクセス時間が短い順に並べたものはどれか。

ア A, B, C, D イ A, D, B, C

ウ C, D, A, B エ D, C, A, B

正解は”イ”

それぞれの実効アクセス時間は以下の通りです。

A:15ナノ秒

B:30ナノ秒

C:20ナノ秒×0.6+70ナノ秒×0.4=40ナノ秒

D:10ナノ秒×0.9+80ナノ秒×0.1=17ナノ秒

平成30年度春期問11

基本情報技術者

午前試験 平成30年度春期問11

キャッシュメモリに関する記述のうち,適切なものはどれか。

ア キャッシュメモリにヒットしない場合に割込みが生じ,プログラムによって主記憶からキャッシュメモリにデータが転送される。

イ キャッシュメモリは,実記憶と仮想記憶とのメモリ容量の差を埋めるために採用される。

ウ データ書込み命令を実行したときに,キャッシュメモリと主記憶の両方を書き換える方式と,キャッシュメモリだけを書き換えておき,主記憶の書換えはキャッシュメモリから当該データが追い出されるときに行う方式とがある。

エ 半導体メモリのアクセス速度の向上が著しいので,キャッシュメモリの必要性は減っている。

正解は”ウ”

平成29年度春期問9

基本情報技術者

午前試験 平成29年度春期問9

キャッシュの書込み方式には,ライトスルー方式とライトバック方式がある。ライトバック方式を使用する目的として,適切なものはどれか。

ア キャッシュと主記憶の一貫性(コヒーレンシ)を保ちながら,書込みを行う。

イ キャッシュミスが発生したときに,キャッシュの内容の主記憶への書き戻しを不要にする。

ウ 個々のプロセッサがそれぞれのキャッシュをもつマルチプロセッサシステムにおいて,キャッシュ管理をライトスルー方式よりも簡単な回路構成で実現する。

エ プロセッサから主記憶への書込み頻度を減らす。

正解は”エ”

平成28年度春期問11

基本情報技術者

午前試験 平成28年度春期問11

キャッシュメモリの効果として,適切なものはどれか。

ア 主記憶からキャッシュメモリへの命令の読出しと,主記憶からキャッシュメモリへのデータの読出しを同時に行うことによって,データ転送を高速に行う。

イ 主記憶から読み出したデータをキャッシュメモリに保持し,CPUが後で同じデータを読み出すときのデータ転送を高速に行う。

ウ 主記憶から読み出したデータをキャッシュメモリに保持し,命令を並列に処理することによって演算を高速に行う。

エ 主記憶から読み出した命令をキャッシュメモリに保持し,キャッシュメモリ上でデコードして実行することによって演算を高速に行う。

正解は”イ”

基本情報に関するの他の記事

| ハードウェア | ソフトウェア | システム構成 |

| ネットワーク | データベース | 開発手法 | 情報セキュリティ |

ハードウェアに関する記事

基数についての記事

【基本情報】コンピュータが理解できるのは0と1だけ?!

【基本情報】2進数と10進数を変換する方法を解説

【基本情報】2の補数について分かりやすく解説!

【基本情報】16進数とコンピュータは相性が良い

【基本情報】16進数と10進数を変換する方法を解説

情報の単位についての記事

【基本情報】ビットとバイトとは何か、1バイト=8ビットの理由も解説

論理演算についての記事

コンピュータの五大装置についての記事

【基本情報】コンピュータってなにで出来ている?-五大装置を解説

【基本情報】クロック周波数とは?なぜ必要なの?

【基本情報】RAMとROMの特徴と違いについて解説

【基本情報】キャッシュメモリについて解説